Existen diversos tipos de arquitectura de computo a través del recorrido de la historia computacional dentro de la cuales podemos mencionar las siguientes como pilares fundamentales.

- Arquitecturas Clásicas

- Arquitectura Mauchly-Eckert (Von Newman)

- Arquitectura Harvard.

- Arquitecturas Segmentadas.

- Arquitecturas de multiprocesamiento.

- SISO

- SIMO

- MISO

- MIMO

La arquitectura Eckert-Mauchly (publicada por John von Neumann y

la más utilizada) describe una computadora en 4 secciones principales:

Unidad aritmetica logica (ALU): calcula operaciones aritmeticas

(como adicion, substracción, etc.) y operaciones lógicas (como OR,

NOT, XOR, etc.)

Unidad de control: encargada de activar o desactivar los diversos

componentes del microprocesador en función de la instrucción que el

microprocesador esté ejecutando

Memoria central: dispositivos y medios de grabación que retienen

datos informáticos durante algún intervalo de tiempo

Dispositivos de entrada y salida (E/S): dispositivos de

comunicación con el exterior.

Esta arquitectura es la más empleada en la actualidad ya, que es muy versátil. Ejemplo de esta

versatilidad es el funcionamiento de los compiladores, los cuales son programas que toman como

entrada un archivo de texto conteniendo código fuente y generan como datos de salida, el código

maquina que corresponde a dicho código fuente (Son programas que crean o modifican otros

programas). Estos datos de salida pueden ejecutarse como un programa posteriormente ya que se usa la

misma memoria para datos y para el código del programa.

La principal desventaja de esta arquitectura, es que el bus de datos y direcciones único se convierte en

un cuello de botella por el cual debe pasar toda la información que se lee de o se escribe a la memoria,

obligando a que todos los accesos a esta sean secuenciales. Esto limita el grado de paralelismo

(acciones que se pueden realizar al mismo tiempo) y por lo tanto, el desempeño de la computadora.

Este efecto se conoce como el cuello de botella de Von Newman.

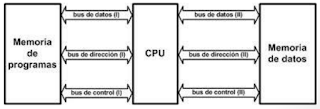

Arquitectura Harvard se utilizan dispositivos de almacenamiento (memorias)

separados para las instrucciones y los datos, y tiene dos sistemas completos de

buses, uno para datos y otro para instrucciones. Esta arquitectura perite llevar

simultáneamente datos e instrucciones por lo que permite mayor rapidez.

El hecho de tener un bus separado para el programa y otro para los datos permite que se lea el código

de operación de una instrucción, al mismo tiempo se lee de la memoria de datos los operados de la

instrucción previa. Así se evita el problema del cuello de botella de Von Newman y se obtiene un mejor

desempeño.

Comparacion entre Harvard y Neuman

Las arquitecturas segmentadas o con segmentación del cauce buscan mejorar el desempeño realizando

paralelamente varias etapas del ciclo de instrucción al mismo tiempo. El procesador se divide en varias

unidades funcionales independientes y se dividen entre ellas el procesamiento de las instrucciones. Para

Procesador Memoria de datos

Entrada y salida

Bus de

datos

Memoria de

programa

Bus de

programa

Registros

ALU

Unidad de

Control

comprender mejor esto, supongamos que un procesador simple tiene un ciclo de instrucción sencillo

consistente solamente en una etapa de búsqueda del código de instrucción y en otra etapa de ejecución

de la instrucción.

En la segmentacion la ejecución de una instrucción pasa por varias etapas:

1. Búsqueda de Instrucción.

2. Decodificación.

3. Búsqueda de Operandos.

4. Ejecución.

5. Almacenamiento de Resultados.

Mejora dramáticamente el rendimiento debido a que en los procesadores modernos tienen hasta 14 etapas en el ciclo de instrucción.

La unidad de control se subdivide en dos o más unidades funcionales, cada una encargada de llevar a cabo una parte del ciclo de instrucción.

Se comunican a través de una cola de instrucciones (Pipeline)

Arquitecturas multiprocesamiento construidas con dos o más

procesadores, esto nos permite ejecutar de manera simultánea varios procesos,

su ventaja reside en la operación llamada cambio de contexto que consiste en

quitar un proceso de la CPU, ejecutar otro y volver a colocar el primero sin que

se entere de nada. Los dos objetivos primordiales de los multiprocesadores son

acelerar la ejecución de aplicaciones orientadas a la supercomputación y

ejecutar más aplicaciones por unidad de tiempo.

Los sistemas multiprocesadores tienen dos modelos de organización:

. Los de memoria compartida, que permiten, a través de la red de

interconexión, que cualquier procesador acceda a cualquier posición de

memoria, sin embargo en este tipo de multiprocesadores, la red de

interconexión es un cuello de botella lo cual impide que sea escalable.

Los de memoria distribuida, donde la red de interconexión permite que

cualquier procesador se comunique con cualquier otro del sistema. Los sistemas multiprocesadores, pero en especial los de memoria distribuida,

tienen una gran potencia de cálculo y al paso del tiempo esta

característica sigue aumentando. La figura 2 muestra la estructura de

este tipo de sistemas.

Las CPU de multiprocesamiento se clasifican de la siguiente manera (Clasificación de Flynn):

SISO – (Single Instruction, Single Operand ) computadoras Monoprocesador

SIMO – (Single Instruction, Multiple Operand ) procesadores vectoriales, Exenciones MMX

MISO – (Multiple Instruction, Single Operand ) No implementado

MIMO – (Multiple Instruction, Multiple Operand ) sistemas SMP, Clusters, GPUs .

La nueve tendencia en Arquitecturas de computo procesadores vectoriales son computadoras pensadas para aplicar un mismo algoritmo numérico a

una serie de datos matriciales, en especial en la simulación de sistemas físicos complejos, tales como

simuladores para predecir el clima, explosiones atómicas, reacciones químicas complejas, etc., donde

los datos son representados como grandes números de datos en forma matricial sobre los que se deben

se aplicar el mismo algoritmo numérico.

Como su nombre implica, los procesadores vectoriales se ocupan de múltiples

datos en el contexto de una instrucción, contrastando con las CPUs más comunes de

hoy en día que tienen procesadores escalares/superescalares y tratan un dato por cada

una. A estos dos esquemas se les conoce respectivamente como SISD (Single

Instruction, Single Data) que se corresponde con la arquitectura Von Neumann y

SIMD (Single Instruction, Multiple Data) que es una técnica empleada para

conseguir paralelismo a nivel de datos. Esta clasificación recibe el nombre de

taxonomía de Flynn.

Casi todas las CPUs de hoy en día incluyen algunas instrucciones de

procesamiento de tipo vectorial. En particular y como se verá más adelante,

dispositivos móviles, consolas de videojuegos, tarjetas gráficas, etc hacen un uso

intensivo de este tipo de procesamiento.

Un procesador vectorial (vector processor o array processor) es una CPU queejecuta instrucciones que operan sobre un array unidimensional de datos (un vector).Una máquina vectorial consta de una unidad escalar segmentada y una unidad vectorial. La unidad vectorial dispone de M registros vectoriales de N elementos y deunidades funcionales vectoriales (de suma, resta, multiplicación, división, decarga/almacenamiento, etc) que trabajan sobre registros de ese tipo.El juego de instrucciones de este tipo de procesadores es evidentemente tambiénvectorial. Un ejemplo de instrucción vectorial sería addv v1,v2,v3, es decir, unaoperación vectorial que equivale a un bucle escalar completo que procesaría los N elementos del registro vectorial.

Referencias

http://www.tdx.cat/bitstream/handle/10803/3038/fgt1de2.pdf?sequence=1

http://www.atc.uniovi.es/inf_superior/4atc/trabajos/paralelas/2-Procesadores%20Vectoriales%20comerciales-memoria.pdf

http://rvazquez.org/Misitio/Arquitectura_de_Computadoras_files/unidad2arqcom.pdf

http://www.frbb.utn.edu.ar/hpc/lib/exe/fetch.php?media=2017-02-aquitecturas.pdf

http://www.aliat.org.mx/BibliotecasDigitales/sistemas/Arquitectura_de_computadoras_II.pdf

http://profesores.fi-b.unam.mx/luist/archivos/MicroprocesadoresSavage.pdf

http://personales.upv.es/pabmitor/acso/FILES/ArqComp/CST/ArqComp%20t4.pdf

No hay comentarios:

Publicar un comentario